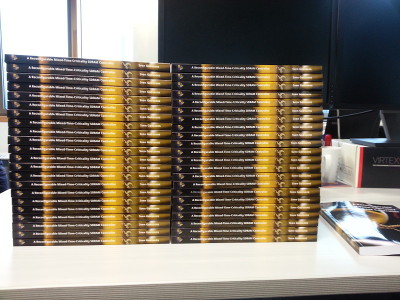

Four years and a few months of hard work condensed into 213 pages, and this is what it looks like:

128 copies (a nice round number) of my thesis `A Reconfigurable Mixed-Time-Criticality Memory Controller’ are ready to be distributed to everyone who is interested.

My Ph.D. thesis is about real-time memory controllers, and more specifically, pattern-based memory controllers. Such controllers need to be programmed with memory patterns, which are sequences of SDRAM commands that are executed by the controller when it needs to read from or write to the memory. You can read about how these patterns are used in this article on ieeexplore. The SDRAM controller in the CompSOC platform executes these memory patterns, enabling us to give (real-time) guarantees on worst-case bandwidth and worst-case response time.

Patterns are statically computed at design time, and since this is quite a tedious process to do manually, we automated it with a publicly available tool, which you can find on the gitlab page of our group. This post describes the pypatterngen tool that creates SDRAM command schedules for DDR2/3/4 and LPDDR1/2/3 that satisfy the SDRAM timing constraints.

Continue reading